×

×

×

×

封装在向更高功率密度的过渡中发挥着越来越重要的作用,从而实现更高效的电源、电力传输、更快的转换以及更高的可靠性。随着全球转向更快的开关频率和更高的功率密度,用于基板、芯片贴装、引线键合和系统冷却的材料也发生了相关的变化。

英飞凌中功率电压 MOSFET 总监 Brian LaValle 在最近的一次网络研讨会上表示:“随着我们在硅本身方面取得进步,封装开始变得越来越重要。”

在高功率和高电流方面,电源模块提供分立封装和集成模块,根据设备规格和使用条件为制造商提供竞争优势。领先的公司供应数百种分立功率器件,但其中一些最常见的包括通孔封装,例如带长银引线的 TO-247 和 TO-220,以及带引线的表面贴装 (SMT) 元件,例如D2PAK、DPAK、SO-8 和无引线 (TOLL)、PQFN 和 CSP。

顶部冷却 SMT 可以提供较低的热阻,因为排水片直接连接到散热器。由于 SMT 中的栅极环路更小,该方法还可以提高开关性能。暴露的源极片可以与散热器齐平,以提高器件的电流能力。整体解决方案包括通过单面或双面冷却进行有效的热管理,以及框架或模制模块中的多芯片集成。

据 Amkor 称,功率四方扁平无引线 (PQFN) 封装是当今最受欢迎的选择之一。这是由于其紧凑的尺寸(3 x 3mm 至 8 x 8mm)、低寄生效应(可实现极低的导通电阻 [RDS(on)])、出色的热性能以及众多的多芯片、多夹子和电线变化。PQFN 还与 GaN 兼容,并且具有无铅电镀和无卤素模塑料、汽车用可润湿侧翼以及双散热器选项。

Amkor 还使用多种 SiC 兼容工艺,其中包括体积 SiC 切割、大规格引线键合以及符合汽车标准的测试和老化服务。“Amkor 是首批为电动汽车制造商提供碳化硅封装的 OSAT 之一,” Amkor焊线和电源业务部公司副总裁 Sivakumar Mohandass 说道。“我们为所有电源解决方案提供测试和老化服务,为客户提供交钥匙解决方案。”

驱动器和应用

功率器件是在电子系统中启动、停止或调节功率的晶体管和二极管。电力电子产品在我们的生活中无处不在,而净零排放的推动预计将在短短几年内(2025/2026 年)将市场规模从 2022 年的 220 亿美元增加一倍至 440 亿美元。事实上,麦肯锡估计 2022 年至 2030 年间,仅碳化硅功率器件的复合年增长率就达到 26%。

分立功率器件和功率模块用于交通、电网、能源存储、计算、5G 基础设施、充电器和工业驱动等领域。新功率封装(包括测试)市场占整个半导体功率市场的20%至25%。

设备分为低电压、中电压和高电压类别,与低电流、中电流和高电流密切相关。就在十年前,计算驱动器的额定电压为 30V 和 40V 仍是常态。如今的电压等级范围为 40V 至 150V。这一变化正在推动从硅 MOSFET 和 IGBT 向基于碳化硅 (SiC)和氮化镓 (GaN) 的转变,后者的宽带隙能够以更小的尺寸实现更高的开关功率特性、更高的工作频率和更低的 RDS(on)。脚印。[注:绝缘栅双极晶体管将输入 MOSFET 与输出双极结型晶体管结合在一起。]

在智能电源应用中,效率是最重要的选择因素。相比之下,汽车应用要求功率损耗保持在绝对最低水平。SiC 器件的工作温度较高,且与硅系统价格相当,这使得 SiC 成为电池电动汽车车载充电、牵引逆变和 DC-DC 转换的首选材料。

电源开关非常高效,但即使是最高效的开关也需要权衡操作。封装电感和电阻直接影响传导和开关损耗。

功率器件的结构与 CMOS FET 不同。它们是垂直器件而不是平面器件,并且它们不像 CMOS 器件那样缩放。尽管如此,还是有一些方法可以实现有效的扩展。QP 高级工艺工程师 Sam Sadri 表示:“尽管在微流体冷却方面有很多研发活动,但您可以通过使用直接键合铜 (DBC) 连接两个相同的芯片并从两侧对其进行冷却(目前通常使用气流)来减小尺寸。”技术。

直接键合铜通常是一个两层工艺,其中基板的背面是坚固且无特征的铜片,并且顶部铜层使用湿化学蚀刻来结构化以形成电路迹线。底部铜层通常焊接到散热器或散热器上。

对于电源模块等复杂器件,设计技术与工艺技术的协同优化变得越来越普遍。Synopsys、Cadence 和其他 EDA 公司在系统设计规划之初就推荐对设备使用 DTCO。例如,Synopsys PrimePower 产品能够对块级和全芯片设计进行准确的功耗分析,从 RTL 开始,经过不同的实施阶段,直至功耗签核。该实现包括由 RTL 和门级活动驱动的门级功耗分析以及详细的功率级可靠性签核。

芯片尺寸越大,与不同材料特性相关的机械挑战就越大,特别是热膨胀系数 (CTE)。功率模块在较高的结温下运行,反复达到 150°C 至 200°C,这对材料造成了压力。“还有电气要求,例如环路电感。例如,当您设计电源时,您必须了解电气特性,因为在正常情况下可能不会出现问题。但当出现电涌时,可能会发生损坏,”QP Technologies 的 Sadri 说道。“另一个显然是机械特性。当 CTE 不匹配时,当两种材料加热和冷却时,它们会以不同的速率膨胀和收缩,从而产生机械应力 - 例如,硅的 CTE 约为 4,而铜的 CTE 约为 17 (ppm/°C)。”

汽车逆变器和其他应用中用 SiC MOSFET 取代硅 IGBT 也正在推动装配和封装的变化。由于其工作温度较高,因此需要大规格引线键合、铜夹、银烧结和导电性更强的模塑料。SiC 的硬度几乎与金刚石一样,因此分割会使用这种材料(金刚石涂层刀片)来机械分离芯片。3D-Micromac 开发了一种速度更快且潜在破坏性更小的工艺,该工艺在两步划线和切割工艺中使用热激光锯切 (TLS-Dicing) 工艺。

快如闪电的开关

电力电子设备由电源转换开关组成,这些开关将电池电量转换为电力驱动电机,以及用于管理和减少非电动汽车燃油消耗和排放的动力系统解决方案。功率器件(MOSFET 或 IGBT)可以是分立(单操作)器件或集成模块,属于系统级封装 (SiP) 的一种。

功率器件的运行总是会产生损耗,包括传导损耗和开关损耗。随着功率半导体制造商向更高功率密度发展,在高结温下损耗可能高达 100V/cm2。所有绝缘材料和互连方法的设计必须保证系统在规范范围内运行。

功率器件运行的敌人是寄生电阻、电容和电感,通常统称为“寄生效应”。除了普遍转向 SiC 和 GaN 技术之外,功率封装可以是分立的,也可以是集成的,如模块中的电源管理 IC 或 PMIC。这些模块可以是基于框架的或模制的。

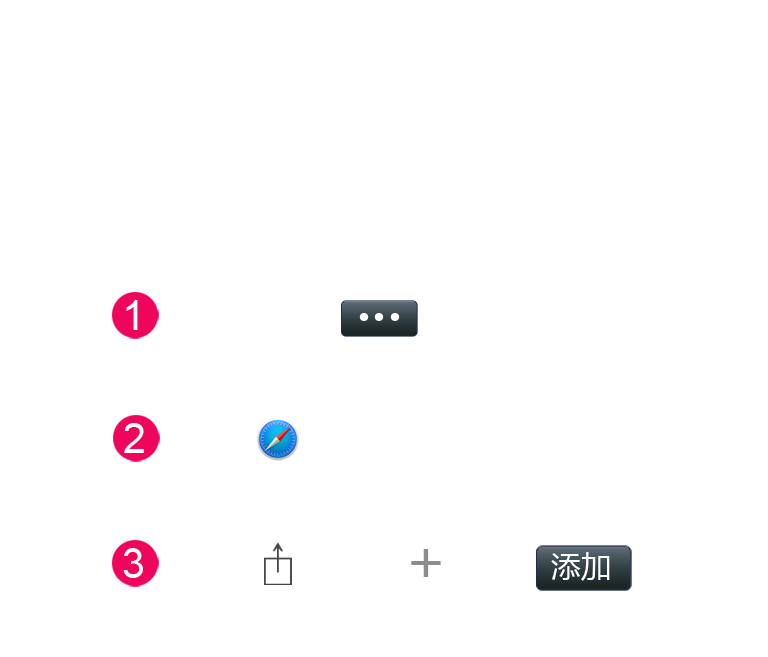

功率器件封装为器件提供电压隔离、电气连接、机械稳定性、防潮和散热。当需要多个芯片时,将它们并联连接在一个模块中。例如,用于牵引逆变器的功率模块具有高电压和高电流能力(高达 10kV),采用了覆铜陶瓷基板。该布局使用楔形铝键合将电位和正面接触分开(见图 1)。

氮化铝的导热性最好,但机械强度较差。氧化铝(Al 2 O 3 )最便宜,但导热率低。高达 3 电平拓扑的超大电流需要多个基板,例如,在尺寸为 50mm x 60mm 的汽车牵引模块中(3.3kV,I nom为 1.5kA)。基板可以是铜或铝银铜合金。Infineon 的 Olaf Holfeld 指出,100W/cm 2的损耗密度和 150 至 200°C 的运行温度很常见。

图 1:框架式功率模块采用金属基板、陶瓷基板、引线键合和铜端子。空腔内填充有硅胶,起到绝缘作用

多年来,芯片连接材料已从含铅焊料变为烧结银。烧结是一种利用温度(在许多情况下还利用压力)将纳米级颗粒粘合在一起,同时连接相邻表面的过程。也可以使用铜进行烧结。英飞凌估计,烧结银芯片连接的粘合可靠性比传统焊料高 20 倍。对于引线键合,将根据长度选择铝或铜,但铜可以处理的电流是银的两倍。

芯片与基板连接的可靠性取决于堆栈承受功率循环和温度波动的能力。东洋油墨最近推出了一种纳米银芯片粘接材料,该材料在汽车应用中表现出 300W/mK 的导热率和 40 MPa 的粘合强度。它在 230° 至 300°C 的温度下使用无压或压力辅助条件进行点胶。同时,烧结银浆可以承受更高的工作温度,并且比传统焊料具有更薄的粘合层厚度。

“烧结银含有如此多的银,其性能比金锡或焊料好得多,而金锡或焊料是连接功率芯片的典型方法,”QP Technologies 的 Sadri 说。

尽管用于功率器件的封装技术有多种,但工程师会选择与芯片性能规格(比电阻、Rds(on) 和栅极电流)最匹配的架构、互连和组装方法,而成本几乎始终是一个重要因素因素。

对于复杂的器件类型,设计技术与工艺技术的协同优化变得越来越普遍。Synopsys、Cadence 和其他 EDA 公司在系统设计规划之初就推荐对设备使用 DTCO。Synopsys PrimePower 产品能够对块级和全芯片设计进行准确的功耗分析,从 RTL 开始,经过不同的实施阶段,直至功耗签核。

与 DTCO 一样,可制造性设计 (DFM) 对于功率器件至关重要。“工程师可以制造任何东西。但我们需要构建数千甚至数百万台具有相同性能和可靠性的设备。因此,这就是 DFM 真正重要的地方,这是关键,”Sadri 补充道。

嵌入式基板方法

工程师可以最大限度地减少寄生效应的方法之一是使用嵌入式芯片基板。在此,功率器件(MOSFET、IGBT)和无源器件集成在基板(有机层压层的堆叠)中,并使用基板中的镀铜通孔和导电迹线进行连接。较短的互连可以最大限度地减少失真和功率损耗,同时降低电阻和热阻。

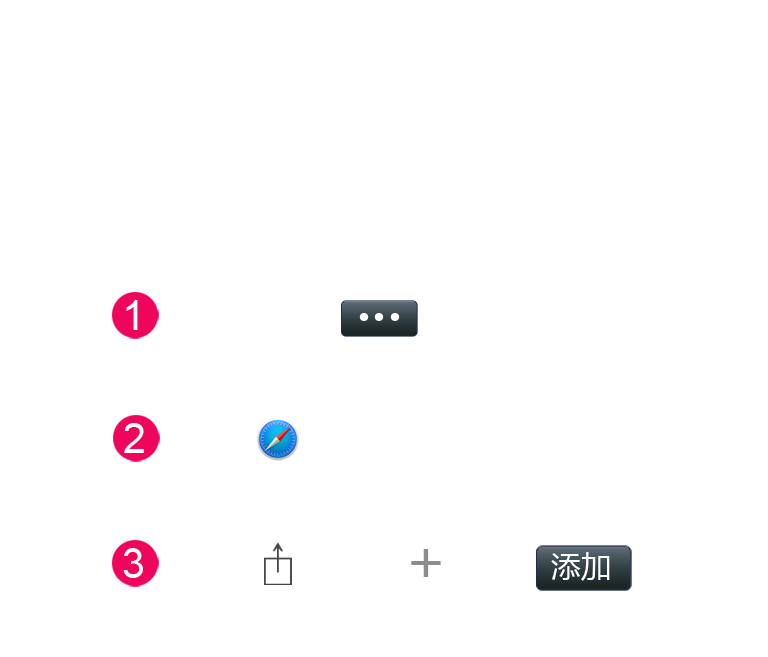

图 2:嵌入式基板方法通过将器件、引线框架和基板集成在一起来降低功耗,从而减少寄生效应,提供高散热和 EMI 优势

嵌入式技术提供 SMT 集成和灵活的布线解决方案。铜通孔结构提供短连接路径,所应用的金属引线框架和芯片布局可以实现高散热和 EMI 优势。

例如,ASE 的 a-EASI(高级嵌入式主动系统集成)方法旨在以较小的占地面积实现更高水平的功能集成。该方法可以表面贴装 (SMT) 到 PCB 上,并提供布线灵活性以减小总体 PCB 尺寸。

随着历史悠久的硅器件被具有更快开关行为和更高温度能力的 SiC 器件所取代,功率半导体组装中使用的材料正在发生变化。封装公司开始采用无引线封装,例如 TOLL 或功率 CSP,以及空间关键型应用中的表面贴装器件。

随着当前对纯电动汽车以及太阳能和风能等清洁能源的关注,对可靠电源和转换的需求预计将快速增长。随着碳化硅功率器件性能和可靠性的提高,烧结银和直接键合铜等材料将越来越多地被采用,以在更小的整体占地面积中提供更高可靠性的电力系统。